Products

GG网络技术分享 2025-03-18 16:08 0

Verilog中generate语句允许在解析阶段(Elaboration-time)对某些语句进行选取或者重复。这些语句可以包括模块实例引用的语句、连续赋值语句、always语句、initial语句和门级实例引用语句等。解析阶段是指仿真开始前的一个阶段,此时所有的设计模块已经被链接到一起,并完成层次的引用。本文将对generate的几种机构进行示例说明.

1.generate语法结构

定义genvar,作为generate种的循环变量。

generate语句中定义的for语句,必须要有begin,为后续增加标签做准备。

begin必须要有名称,也就是必须要有标签,因为标签会作为generate循环的实例名称。

基本结构

genvar 循环变量名;generate

// generate循环语句

// generate条件语句

// generate分支语句

// 嵌套的generate语句

endgenerate可以使用在generate语句中的类型主要有:

1>module(模块)

2>UDP(用户自定义原语)

3>门级原语

4>连续赋值语句

5>initial或always语句

下面将就generate常用的几种情况举例说明。

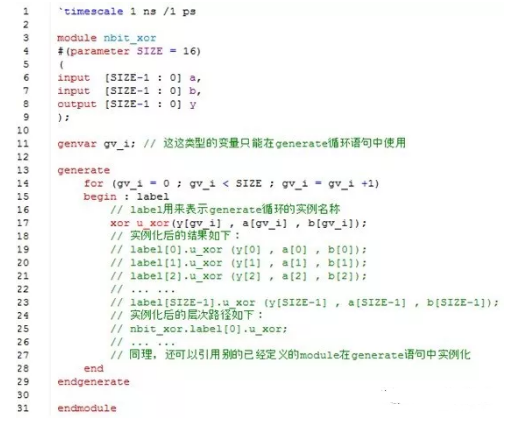

2.generate-loop循环语句

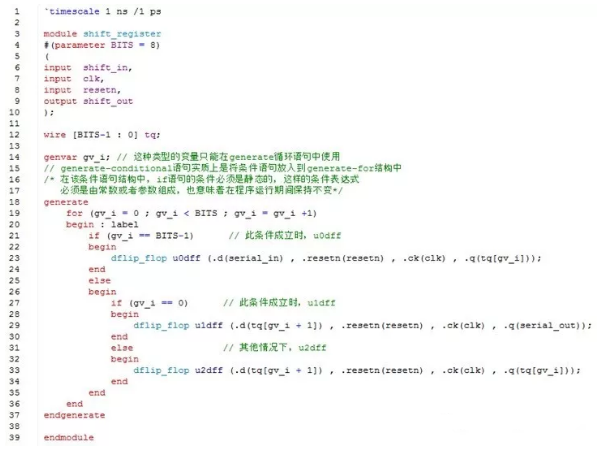

3.generate-conditional条件语句

generate允许对语句进行条件选择,即将条件选择加入到generate中的for循环中,只例化条件成立时对应的语句或者module。

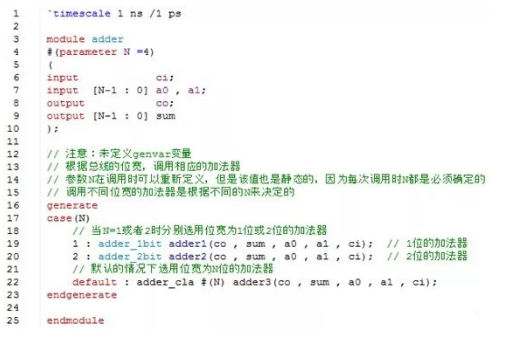

4.generate-case分支语句

generate-case分支语句与generate-条件语句类似,只不过将原来的分支语句换做了case语句。

5.总结

genvar与generate是Verilog2001才有的,功能非常强大,可以配合条件语句、分支语句等做一些有规律的例化或者赋值等操作,对于提高简洁代码很有帮助,同时也减少了人为的影响。

本期分享就到这里,更多IC设计知识请关注叩持电子知乎!

希望可以帮助到你。

Demand feedback